Introduction

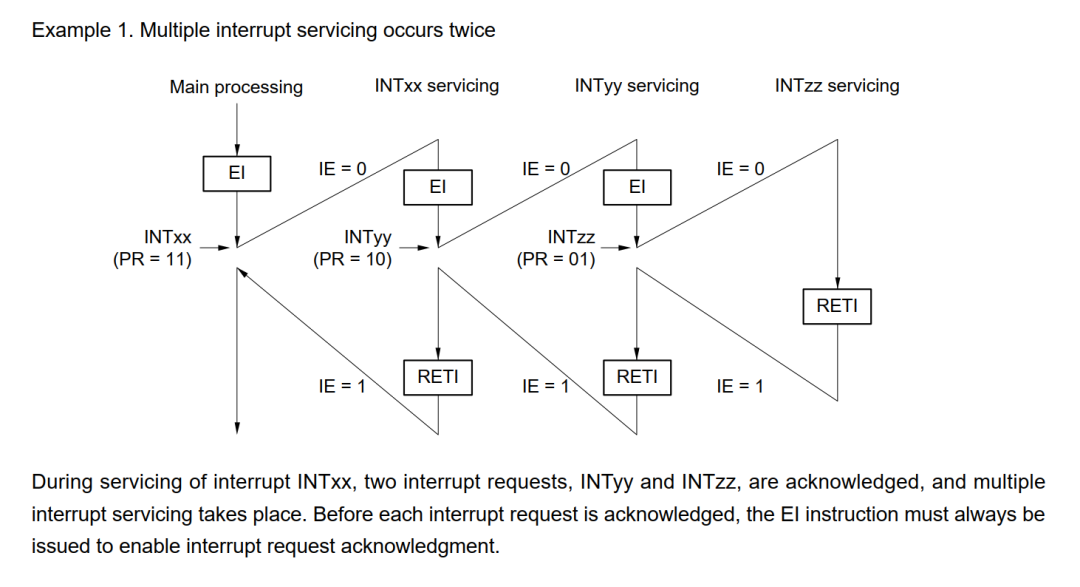

The RL78 series disables interrupt nesting by default, but some applications require improved interrupt responsiveness. For operations with strict real-time requirements, assign higher priorities and enable interrupt nesting so the system can respond to high-priority interrupt requests promptly.

Enabling Interrupt Nesting

According to the chip manual, enable interrupt nesting by re-enabling global interrupts inside the interrupt service routine, as shown below:

RL78 interrupt priority is divided into four levels. Nesting behavior depends on priority: a higher-priority interrupt can preempt a lower-priority one.

Example code is shown here:

Notes on Priority and Vector Order

When two interrupts A and B occur simultaneously: if A has higher priority than B, A is serviced first. If A and B share the same priority level, the hardware interrupt vector table index determines the service order: the smaller index is serviced first.

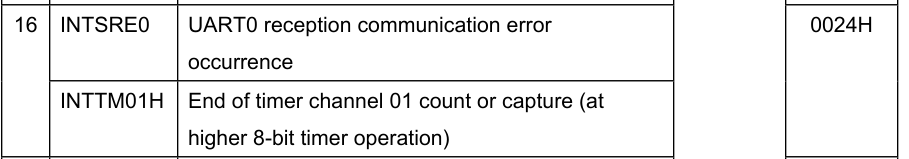

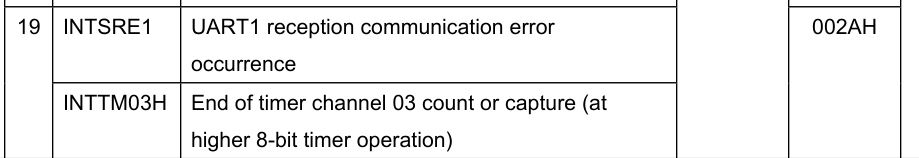

Shared Interrupt Numbers

Some interrupts share the same interrupt number. For example, interrupt number 16 is shared by UART0 receive error and Timer 1 high-order interval interrupt. It is recommended to use only one of these sources for that interrupt number. If both must be used, distinguish them within the same ISR by checking status flags.

Fixed Interrupt Vectors and Bootloader Considerations

RL78 hardware interrupt vectors are located at fixed addresses and cannot be redirected. Special care is required when implementing a bootloader. Application interrupt handling must be implemented via a secondary jump.

Conclusion

RL78 MCUs support interrupt nesting, but remember: only higher-priority interrupts can preempt lower-priority ones. Lower-priority interrupts cannot preempt higher-priority ones, and interrupts at the same priority cannot preempt each other.

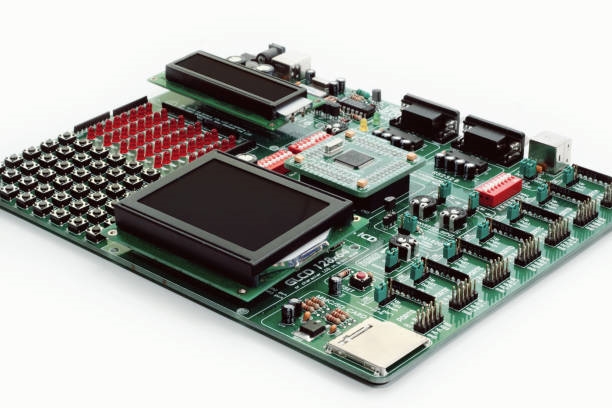

ALLPCB

ALLPCB